# AND8139/D

# Ultra-Low Voltage MiniGate<sup>™</sup> Devices Solve 1.2 V Interface Problems

Prepared by: Fred Zlotnick ON Semiconductor

http://onsemi.com

## **APPLICATION NOTE**

Many integrated circuits such as microprocessors and DSPs need to operate at very low voltage in order to conserve power and not over dissipate. Issues arise when the designer has a device, like a DSP, operating at 1.2 V and needs to interface with other semiconductors operating at 3.3 V or more.

When performing the interface between a 3.3 V (or any voltage between 1.2 V and 3.3 V) the one single answer that solves all problems, simply with a minimum of board space, is the NL17SVyyyXV5T2 family. With the six available devices, the signal can be applied to the input and brought to the DSP in the fastest possible time (minimum delay), while occupying minimum board space and consuming minimum power.

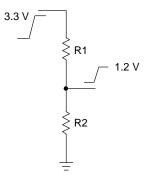

The designer might ask why not simply use resistors to perform voltage division? Resistors can certainly be used for some applications but they consume power and limit the operating frequency and create a delay (when the designer includes the C of the input device). Figure 1 illustrates the use of two resistors to limit the voltage on the DSP. For simplicity, this article will not take into account tolerance issues. That will be left to the reader if he chooses this approach. In all cases, we will use  $V_1 = 3.3$  V,  $V_2 = 1.2$  V, f = 35 MHz, and  $C_{IN} = 10$  pf. If 640  $\Omega$  and 330  $\Omega$  resistors

Figure 1.

are used, the circuit will perform the required voltage division. The loading will be 330  $\Omega$  and draw 1.0 mA when the device is on. If it is assumed to be a 50% duty cycle, then the power consumption for the simple resistor divider will be 16 mW. This power consumption is so high that it would be ruled out immediately. If we would have used larger value resistors, the frequency response would be impaired and 35 MHz would be impossible. The delay time through this circuit will be about 15 to 20 ns.

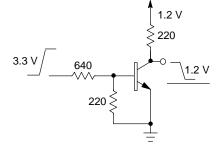

A second possible scheme might be to use a transistor. If an NPN transistor were used, it would need a voltage division scheme similar to Figure 1 and the values would need to be the same in order to keep the frequency response to > 50 MHz  $f_{3dB}$ . Power dissipation would be actually higher than for the passive case because we would have a third resistor from 1.2 V to the collector (Figure 2). We would have another 5.0 mW of power dissipation due to the output resistor. This solution would consume > 20 mW of power and again is outrageously high in the power budget. In addition, the manufacturer would have to place three parts (three resistors and one transistor or one BRT plus one resistor). Delay time would be longer than the passive solution above, hence more costly and would present absolutely no advantage over the simple resistive divider.

Figure 2.

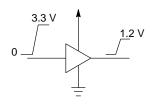

It should be noticed that the signal is inverted for the case of the transistor. This may or may not be desirable. In fact, the phase inversion would be the only plausible reason to prefer the transistor case over the passive resistor divider. The last option that will be presented will be the ON Semiconductor sub-one volt family, NL17SVxx products. We have the choice of inverted or non-inverted output. Since the devices are Over-Voltage Tolerant (OVT) at their inputs, the designer may simply apply the 3.3 V signal to the input of the device. For this application, Figure 3 shows the supply voltage to the device will be 1.2 V. This assures that the output will be logic level compatible with the device that it is driving.

NL17SV16XV5T2 Figure 3. Since the 3.3 V logic is only driving a capacitive input, there is very little power dissipation at the input. To calculate the total power consumed, we must use a different equation that depends on the Power Dissipation Capacitance ( $C_{PD}$ ) as the main factor. To calculate the power loss in the gate, the following formula is used:

$$PD = (C_{PD} \cdot V_{CC}^2 \cdot f) + (I_{CC} \cdot V_{CC})$$

At 35 MHz and  $C_{PD}$  of 20 pf, the equation works out to ~ 2.0 mW total power, with about 50% of the power consumed in leakage current and 50% in the switching. The delay time is only 10 ns (worst case), at V<sub>CC</sub> of 1.2 V.

### Conclusion

The use of a single gate for logic level translation saves 90% of the power required for a passive solution and even more compared to a transistor solution. The manufacturer needs only to place one part versus two or more for any other approach. The time delay is much faster and less circuit dependent. Output may be either inverted or non–inverted (by selecting appropriate single gate device). The circuit will easily operate past 50 MHz, if needed at 1.2 V. It is clear that this is the only practical solution for logic level translation at low power.

MiniGate is a trademark of Semiconductor Components Industries, LLC.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.